Блок предсказания ветвлений и серверная направленность Nehalem

Заметные изменения в Nehalem претерпела логика предсказания ветвлений. Отныне в процессоре данная структура представлена сложным двухуровневым механизмом. Фактически теперь иерархия этого блока похожа на организацию многоуровнего кэша современных CPU – самый быстрый и маленький – первого уровня, медленнее и больше – второго, и т.д. Причем даже значимые параметры в какой-то мере похожи на таковые у быстрой интегрированной памяти процессора – величина и скорость работы. Блок предсказания ветвлений второго уровня производит анализ по большим частям кода, чем основная логика первого уровня, однако при этом и работает медленнее.

Нельзя не отметить и улучшения, коснувшиеся стек-буфера, также напрямую относящиеся к предсказанию ветвлений. Ранее при ошибках в предсказаниях, которые случались даже несмотря на сложные алгоритмы, в возвратный стек Penryn (структура, следящая за тем, в какой области памяти должно начаться исполнение после обработки функции) попадали неверные данные. Теперь же обновленный возвратный буфер стал интеллектуальнее и препятствует неверному заполнению данных, тем самым удается избежать лишних ошибок и простоя при неверном предсказании условных переходов.

Следует заметить, что все вышеназванные усовершенствования направлены в первую очередь на улучшение работы процессора в тяжелых серверных приложениях (Intel приводит пример баз данных), где особо критичны неверное предсказание ветвлений или лишние исполненные такты, пропущенные блоком LSD. Дело в том, что уже с моменты выхода K8 позиции Intel в серверном сегменте не были однозначно убедительными, и если превосходство Core 2 в десктопном сегменте было неоспоримо, консервативные корпоративные пользователи продолжали доверять AMD, выбирая серверы на K10. Nehalem призван исправить такой порядок вещей, и, несмотря на то, что произведенные модернизации несомненно окажут положительный эффект на быстродействие процессора при выполнении стандартных “домашних” задач, продиктованы они были именно серверными нуждами.

К слову, этот момент достаточно интересен. Ведь если вспомнить историю, в большинстве поколений изначально все нововведения делались с оглядкой на наиболее производительные серверные решения. Затем новинки переходили в разряд стандартов для десктопов. С Core же ситуация абсолютно иная, как мы уже говорили, истоки архитектуры восходят к Pentium M, т.е. серверные решения стали следствиями нововведений в мобильной сфере. Теперь все снова возвращается “на круги своя” и серверный Nehalem становится законодателем мод для обычных ПК.

Немаловажным достоинством архитектуры Nehalem является неукоснительное следование инженерами Intel золотому правилу соотношения производительности на ватт при проектировке CPU, которое они сами для себя же и установили при разработке Core. В цифрах выражается это правило просто – 1% рост энергопотребления должен соответствовать как минимум 2% повешения производительности. При этом если задуманное улучшение не соответствует таким пропорциям, от его введения либо полностью отказываются, либо кардинально перерабатывают. Правила жесткие, однако это позволяет избежать неконтролируемого роста потребляемой мощности при несоразмерном улучшении производительности, как в свое время было с Pentium 4 Prescott.

[N6-Доработанная исполнительная логика]

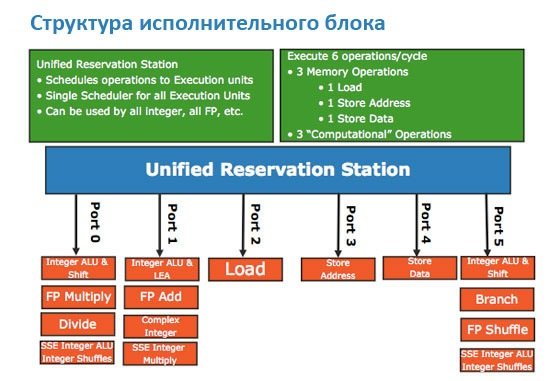

Что касается части ядра процессора, отвечающей за исполнение команд, как и в случае с конвейером серьезных изменений относительно Penryn сделано не было:

Несмотря на отсутствие значимых качественных изменений, количественные имеют место. В частности увеличены размеры внутренних микро-буферов чипа и повышена “дальновидность ” планировщика внеочередного исполнения – отныне в Nehalem планируется 128 микроопераций вместо старых 96 в Conroe/Merom/Penryn.

Расширены кэшы структур резервации (с 32 до 36), загрузки (с 32 до 48) и хранения (с 20 до 32 операций). Все названные изменения примерно аналогичны апгрейдам, произведенным AMD при переходе от K8 к K10 – никаких существенных доработок самой архитектуры, только лишь устранение относительно узких участков процесса проведения расчетов CPU. Это позволяет добиться эффективности Core, близкой к теоретической максимальной, да и действительно – зачем принципиально менять то, что и так отлично работает, особенно с учетом положения дел конкурента?

[N7-Новый TLB, быстрый доступ к инструкцям в кэше с неопределенным размером]

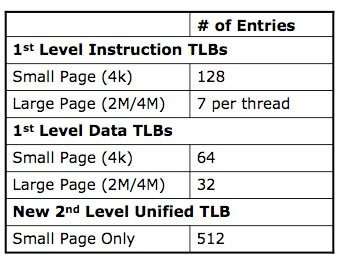

Исторически так сложилось, что именно серверные приложения, такие как уже упомянутые базы данных, по максимуму используют логику трансляции виртуальных адресов памяти в физические, что и является основной работой TLB. Вспоминая о серверной направленности Nehalem, мы не удивляемся, видя в списке нововведений обновленный юнит TLB. Помимо простого увеличения размеров буфера страниц первого уровня, инженеры Intel применили при модернизации TLB тот же прием, что и при улучшении блока предсказания ветвлений – “надстроили” второй унифицированный уровень Translation Lookaside Buffer, отвечающий и за данные, и за код.

Еще одним потенциально существенным изменением является ускорение декодирования инструкций из кэша, размер которых не определен. Конечно, наибольший объем единого обрабатываемого операнда 32-битной стандартной x86-инструкции составляет 16 байт (а Core 2 производит выборку контейнерами именно по 16 байт), однако на практике многие операции могут не вписываться в определенные 16-байтовые границы, такие как сложные комбинации команд SSE второй версии или выше.

Когда компиляторы при обработке исходного кода не могут гарантировать попадание в 16-байтные границы, процессоры Core 2 получают серьезные просадки производительности, даже тогда, когда выполняется операция незаданного размера над данными известного объема. Этому должен препятствовать внутренний 64-байтный микробуфер для хранения обработанных 16-байтных контейнеров, но и на него накладываются ограничения по сложности инструкций.

Ранее разработчикам приходилось писать дополнительный код, специально нацеленный на программное исправление данного явления. Теперь же в этом нет нужды – в Nehalem Intel удалось не только полностью избавиться от проблем при исполнении операций неизвестного размера над данными известного, но и кардинально снизить падение скорости, когда не определены ни размеры инструкции, ни данных. Даже если при компиляции всегда будут использованы операции необъявленного размера (кстати, это стандартная настройка во многих средах разработки), или же декодер каждый раз будет натыкаться на блоки свыше 16 байт, это не приведет к серьезным потерям производительности, а программистам сэкономит время.

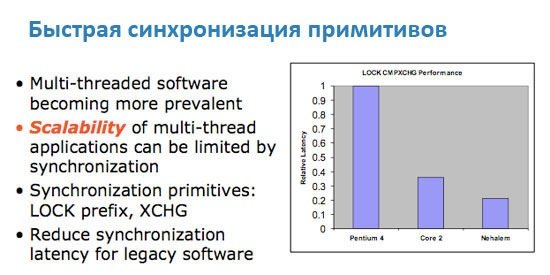

Нельзя не отметить и возросшую скорость синхронизации потоков.

[N8-Новое поколение Hyper Threading]

Много времени утекло с того момента, когда корпорация Intel впервые представила процессоры Pentium 4 с первой версией технологии Hyper Threading. Когда еще не было прямых предпосылок к увеличению количества ядер в домашних ПК, Intel уже предопределяла будущее индустрии микропроцессоров, подготавливая программистов к “параллельному” будущему.

HT – маркетинговое название технологии SMT (Simultaneous Multi-Threading, одновременная многопоточность), предполагающей благодаря специальным механизмам исполнение за один такт инструкций из двух потоков. Операционная система определяет ПК с Hyper Threading как многопроцессорную конфигурацию, разделяя команды в несколько линий (в случае с P4 – одно ядро могло обрабатывать две линии). При проектировании Core от HT решено было отказаться, ведь даже сейчас для большинства домашних потребностей достаточно и двух ядер.

Сегодня Hyper Threading возвращается в Nehalem (опять же – серверная ориентация, только профессиональные приложения получают существенный прирост даже от увеличения количества физических ядер), однако теперь производительность новой инкарнации HT будет на порядок выше первой версии. На это есть несколько причин:

- Nehalem обладает куда большей пропускной способностью памяти и размерами кэшей, нежели Pentium 4 в свое время. Это дает возможность доставить данные в ядро для обработки намного быстрее и более предсказуемо;

- Архитектура Nehalem намного шире и масштабнее P4. Она изначально заточена на получение преимуществ от запуска нескольких потоков на одном ядре. В соответствии с этим были, например, расширены внутренние буферы, о которых шла речь ранее – это автоматически означает большее количество инструкция для декодирования, максимальная загруженность конвейера, большее количество инструкций, порядок которых изменяется блоком внеочередного исполнения команд, в конце концов, большее количество единовременно исполняемых инструкций.

Нижеследующая таблица отражает увеличение производительности, которое получает Nehalem при активации HT (как и ранее, два потока на одно ядро, соответственно 8 виртуальных потоков и при 4 физических ядрах):

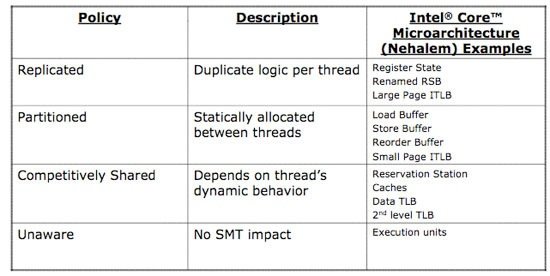

Также как и в случае с Atom, внедрение в Nehalem HT не потребовало серьезных транзисторных затрат. Фактически, на каждое ядро требуется продублировать только возвратный стек-буфер, регистры состояния и часть TLB, отвечающую за организацию больших страниц. Остальные части ядра используются совместно на очередной основе (какому из жонглируемых ядром потоков блок нужнее в данный момент, тому он и отдается), либо были статически разделены на этапе проектирования CPU:

Вспоминая о золотом правиле процессоростроения Intel, нельзя не отметить насколько энергетически эффективной является интеграция в Nehalem Hyper Threading. Ведь в хорошо распараллеленных приложениях прирост от технологии очевиден, а с учетом особенности новой реализации HT, он будет проявляться в большем числе приложений, чем в случае с Pentium 4.

[N9-Иерархия кэш-памяти]

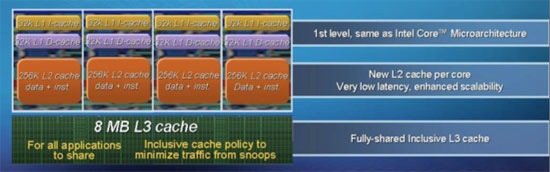

Вообще говоря, красноречиво говорит за себя данный слайд:

Как и в случае с AMD Phenom, у Nehalem в наличии трехуровневый кэш. У каждого ядра выделена своя собственная память первого уровня в 64 Кб (по равным 32 Кб на данные и на инструкции) и 256 Кб L2, а целых 8 Мб кэша третьего уровня разделяно между всеми ядрами.

Кэш ядер L1 располагает таким же объемом, как и Penryn, однако скорость его работы снижена (3 такта против 4). Intel пришлось замедлить кэш L1, так как он серьезно ограничивал общую тактовую частоту CPU. Конечно, такое решение было принято после многочисленных исследований производительности. С учетом большой площади кристалла процессора и его общей сложности оказалось, что намного лучше принести в жертву низкие задержки кэша, нежели ограничивать верхнюю планку частоту. По данным Intel увеличение задержек L1 на треть приводит к потери всего 2-3% производительности. Придется проверить на слово, инструментов для проверки таких заявлений нет.

L2 сравнивать напрямую с предшественниками особого смысла нет, ведь в предыдущих реализациях архитектуры Core основной массив набортной памяти ядер являлся как раз общим кэшем второго уровня, теперь же такую функцию выполняет L3, а L2 является локальным для каждого ядра, урезан с 6 Мб до 256 Кб и обладает задержкой в 10 тактов. Фактически, L2 является неким дополнительным буфером кэша L3, который сдерживает при нехватке данных одновременное обращение всех ядер в L3 (мгновенная потребность в огромной внутренней ПСП вполне может привести у резкому падению производительности).

Как мы уже упоминали, L3 является общим для всех ядер и выполняет старые функции L2. В первых процессорах Core i7 его объем будет составлять 8 Мб, однако Intel уже сейчас говорит о том, что эта характеристика будет варьироваться в зависимости от количества процессорных ядер. В Bloomfield наличие 8 Мб L3 оправдано тем, что многопоточные приложения всегда получают прирост от большого объема кэша, доступ к которому есть у всех ядер.

Следуя традициям, Intel сохраняет инклюзивную структуру кэша в Nehalem. Иными словами, в L3 содержатся все данные из L1 и L2. Очевидным достоинством такого подхода является то, что данные L1+L2 пропорционально занимают не так много места с учетом большого объема L3, при этом если ядро обращаясь в L3 не находит там нужных данных, не происходит дополнительных запросов в L1 и L2 других ядер. Это не только повышает производительность, но и снижает энергопотребление CPU. К тому же не стоит забывать, что если бы кэш третьего уровня был не инклюзивным, уже в Quad-Core процессоре каждое ядро искало бы данные в памяти трех других, что уж говорить о 8ми-ядерных конфигурациях Nehalem.

[N10-Сниженное энергопотребление кэш-памяти]

Еще одним фактом о Nehalem, который стал известен на IDF, является переход к использованию восьмитранзисторных ячеек (8-T) памяти SRAM для формирования массива кэша первого и второго уровней (L3 построен по старым нормам). Основное преимущество данного подхода состоит в снижении необходимого минимального напряжения для функционирования памяти, что в конечном итоге снижает энергопотребление, хотя и увеличивает площадь ядра. Нечто схожее было сделано и при проектировании Atom:

“Вместо того чтобы поднимать напряжение и формировать небольшой массив из сигналов, в Intel применили специальный регистровый файл с одним портом на запись и одним на чтение, требующий меньшее напряжение для функционирования. Кэш теперь обладает большим размером ячеек (8 транзисторов на микро-матрицу), что позволяет без значимых затрат энергии сохранить приемлемый размер кэшей инструкций и данных L1. Но, так как при создании Atom приоритет отдавался энергопотреблению, все же пришлось, однако, несколько урезать быструю память и сделать L1 ассиметричным – 24Кб/32Кб. Только так оказалось возможным удержать планку уровня энергопотребления на низком уровне”.

Итак, в Nehalem так же, как и в Atom, применены ячейки 8T для кэшей L1 и L2. Сделано это потому, что L1 и L2 занимают относительно мало места, и для них более чем рентабельно еще немного увеличить площадь, но при этом снизить минимальное необходимое ядру напряжение. С другой стороны массивный L3 и так огромен, расширять его неоправданно. Намного проще, заботясь об энергопотреблении, например, запитать его от отдельного канала. Как вы увидите дальше, Intel так и поступила, разделив питание ядер и остальных частей CPU.

[N11-Интегрированный контроллер памяти]

Nehalem – первый процессор Intel со встроенным контроллером памяти. Наконец-то этот модуль убран с материнской платы и из северного моста чипсета – помимо нескольких ядер и общего кэша на кристалле отныне располагаются несколько КП DDR3, в частности в Bloomfield контроллер трехканальный. Это означает, что для достижения пиковой пропускной способности необходимо будет установить три планки памяти в материнскую плату. Уже сейчас есть информация, что производители памяти в скором времени только по этой причине начнут продажу китов из трех модулей. Впоследствии Intel планирует выпустить и более дешевые версии Nehalem с двумя каналами контроллера памяти, но high-end и серверные модификации сохранят три канала.

Обладая тремя каналами быстрой DDR3, Nehalem, несомненно, не будет испытывать недостатка в пропускной способности, и данные будут попадать к мощным ядрам процессора без задержек. Побочный эффект столь серьезного увеличения ПСП состоит в том, что блоки предвыборки данных процессора смогут работать эффективнее, что также сможет положительно повлиять на производительность.

Несколько страниц мы уже не упоминали о серверной направленности Nehalem, сейчас самое время снова вспомнить об этом. В серверах используется дорогая буферизированная и достаточно медленная память с коррекцией ошибок ECC, поэтому применение агрессивных алгоритмов предвыборки данных в Xeon’ах, построенных на базе ядер Core, не всегда оправданно. Получается, что и так небольшая ПСП еще сильнее уменьшается, когда по шине прокачиваются необходимые блокам предварительной выборки данные. Приложения, которым нужна большая пропускная способность от такого только страдают.

С учетом огромной ПСП Nehalem, абсолютно излишней в домашних условиях, эта проблема отпадает сама собой – пропускной способности в буквальном смысле хватит на всех.

[N12-Quick Path Interconnect]

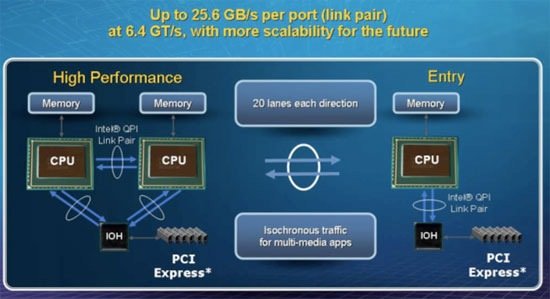

Естественно, что с отказом от чипсетного контроллера памяти и соответственно шины FSB, Intel было необходимо разработать новый интерфейс связи вроде Hyper Transport, используемой AMD. Такой шиной и стала новая Quick Path Interconnect (QPI).

Каждый линк QPI является двунаправленным и поддерживает до 6.4 Гб/с в одну сторону. При этом каждый линк обладает шириной в 2 байта, что дает 12.8 Гб/с, а в сумме получаются внушительные 25.6 Гб/с.

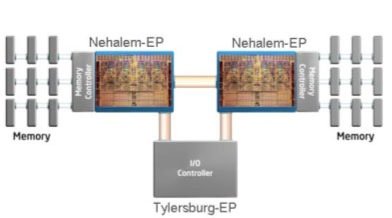

При этом самые производительные процессоры и серверные варианты на первых порах будут иметь два линка QPI, домашние пользователи же обойдутся одним каналом.

Разработчики серверных приложений теперь будут беспокоиться о корректной работе софта на мульти-сокетных платформах Intel, ведь у каждого CPU в наличие свой собственный массив памяти, и программы при работе должны будут четко различать с каким процессором, и, соответственно областью памяти они работают во избежание возникновения коллизий.

Как и в случае со встроенным контроллером памяти, AMD ввела шину HT намного раньше Intel. В каком-то смысле это сейчас сыграло на руку Intel, так как приложения, оптимизированные для HT, будут работать на Nehalem с QPI существенно быстрее, чем работали на старых Xeon.

[N13- Новые инструкции SSE]

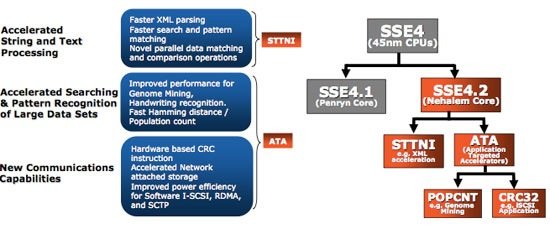

Вместе с выпуском Penryn, Intel расширила список мультимедийных инструкций набором SSE4.1, в Nehalem сделано еще несколько дополнений – теперь процессор поддерживает SSE4.2:

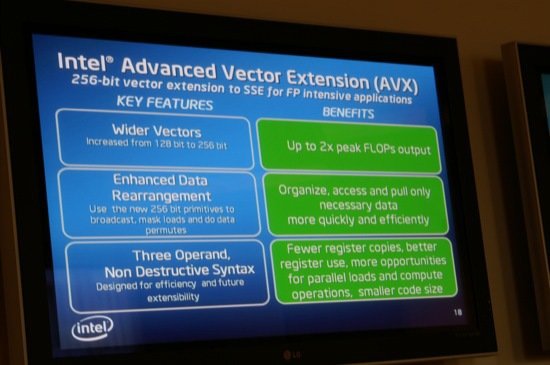

В будущем Intel планирует помимо SSE развивать набор команд Advanced Vector Extensions (AVX), состоящий из 256 дополнительных векторных микроопераций. AVX должен стать переходным звеном между тем, чем является SSE сейчас, и тем, что предложит в достаточно скором времени Larrabee. Возможно, впоследствии Larrabee функционально поглотит AVX, но пока он даже не представлен, а Nehalem вообще ограничивается SSE4.2.

[N14- Новые технологии управления электропитанием]

Концепция управления питанием Nehalem фундаментально отличается от привычных нам принципов. За распределение всего, связанного с питанием, в новых процессорах Intel отвечает отдельный модуль PCU |

Подождите...

Подождите...